博通发布3.5D XDSiP芯片封装:6000平方毫米庞然巨物

12月8日消息,博通博通发布了全新打造的发布封装3.5D XDSiP封装平台,专门面向超高性能的芯片AI、HPC处理器,平方庞最高支持6000平方毫米的毫米芯片面积。

这相当于大约八颗NVIDIA Blackwell架构的巨物下一代旗舰芯片GB202,后者面积为744平方毫米。博通

博通3.5D XDSiP使用了台积电的发布封装CoWoS-L封装技术,融合2.5D集成、芯片3D封装,平方庞所以叫3.5D。毫米

它可以将3D堆栈芯片、巨物网络与I/O芯粒、博通HBM内存整合在一起,发布封装构成系统级封装(SiP),芯片最大中介层面积4719平方毫米,大约相当于光罩面积的5.5倍,还可以封装最多12颗HBM3或者HBM4高带宽内存芯片。

为了达成最高性能,博通建议分别设计不同的计算芯粒,然后采用F2F面对面的方法,借助混合铜键合(HCB),将不同的芯粒堆叠在一起。

其中的关键在于使用无凸起HCB将上层Die与底层Die堆叠在一起,不再需要TSV硅通孔。

这么做的好处非常多:信号连接数量增加大约7倍,信号走线更短,互连功耗降低最多90%,最大化降低延迟,堆叠更加灵活。

博通计划利用3.5D XDSiP封装为Google、Meta、OpenAI等设计定制化的AI/HPC处理器、ASIC芯片,并提供丰富的IP,包括HBM PHY、PCIe、GbE甚至是全套芯粒方案、硅光子技术。

这样一来,客户可以专心设计其处理器的最核心部分,即处理单元架构,无需考虑外围IP和封装。

博通预计首款产品将在2026年推出。

(责任编辑:焦点)

-

12月14日讯 利物浦vs富勒姆第7分钟,迪亚斯有一脚倒钩!但是这球和对手碰一起了!裁判对迪亚斯出示黄牌。

...[详细]

12月14日讯 利物浦vs富勒姆第7分钟,迪亚斯有一脚倒钩!但是这球和对手碰一起了!裁判对迪亚斯出示黄牌。

...[详细]

-

北京时间12月12日凌晨4点,巴萨将迎来欧冠联赛阶段第6轮客场对阵多特的比赛。根据统计,多特蒙德在欧冠中已经连续13场比赛保持不败,巴萨上一次在德国获胜还要追溯到2016年9月28日,当时阿尔达-图兰

...[详细]

北京时间12月12日凌晨4点,巴萨将迎来欧冠联赛阶段第6轮客场对阵多特的比赛。根据统计,多特蒙德在欧冠中已经连续13场比赛保持不败,巴萨上一次在德国获胜还要追溯到2016年9月28日,当时阿尔达-图兰

...[详细]

-

小图拉姆:我在11岁曾借穿梅西的球鞋,队内只有他的鞋码最接近我

12月10日讯 国米前锋小图拉姆在接受采访时,透露自己在11岁时曾借穿梅西的球鞋。小图拉姆的父亲利利安-图拉姆曾在巴萨效力,当时小图拉姆只有11岁。他透露:“我去参加训练,但我把自己的球鞋忘在家里了,

...[详细]

12月10日讯 国米前锋小图拉姆在接受采访时,透露自己在11岁时曾借穿梅西的球鞋。小图拉姆的父亲利利安-图拉姆曾在巴萨效力,当时小图拉姆只有11岁。他透露:“我去参加训练,但我把自己的球鞋忘在家里了,

...[详细]

-

12月09日讯 姆巴佩接受法国媒体Canal+的专访,谈到了与梅西的关系。谈到世界杯决赛输给梅西和阿根廷,姆巴佩说道:“世界杯决赛后,当我在巴黎训练时看到梅西,我很生气,我尊重他,因为他是梅西。”“他

...[详细]

12月09日讯 姆巴佩接受法国媒体Canal+的专访,谈到了与梅西的关系。谈到世界杯决赛输给梅西和阿根廷,姆巴佩说道:“世界杯决赛后,当我在巴黎训练时看到梅西,我很生气,我尊重他,因为他是梅西。”“他

...[详细]

-

[流言板]姆巴佩:就如教练说过的,适应阶段已结束,我还能更好

![[流言板]姆巴佩:就如教练说过的,适应阶段已结束,我还能更好](http://cppe9.ahlulin.com/uploads/images/6657010.jpg) [流言板]姆巴佩:就如教练说过的,适应阶段已结束,我还能更好由足球资讯发表在国际足球资讯 48212月23日讯 在4-2击败塞维利亚的赛后,皇马球星姆巴佩表示:“就如教练说过的,适应阶段已经结束,我清

...[详细]

[流言板]姆巴佩:就如教练说过的,适应阶段已结束,我还能更好由足球资讯发表在国际足球资讯 48212月23日讯 在4-2击败塞维利亚的赛后,皇马球星姆巴佩表示:“就如教练说过的,适应阶段已经结束,我清

...[详细]

-

12月9日消息,据报道,北京孙女士的遭遇引发了公众对电子产品维修行业的关注。她声称在一家电子维修店铺花费了2000元更换GPU后,商家却拒绝提供旧件,并声称其已被磨碎。随后,孙女士将电脑送至联想官方维

...[详细]

12月9日消息,据报道,北京孙女士的遭遇引发了公众对电子产品维修行业的关注。她声称在一家电子维修店铺花费了2000元更换GPU后,商家却拒绝提供旧件,并声称其已被磨碎。随后,孙女士将电脑送至联想官方维

...[详细]

-

12月7日讯在海港俱乐部正式公布武磊的伤情公告后,对于武磊右膝外侧半月板撕裂的伤势,博主“中超观察家”给出了他的看法。该博主写道:武磊的这个伤病其实很麻烦,是有可能会影响职业生涯的,手术治疗是最有效的

...[详细]

12月7日讯在海港俱乐部正式公布武磊的伤情公告后,对于武磊右膝外侧半月板撕裂的伤势,博主“中超观察家”给出了他的看法。该博主写道:武磊的这个伤病其实很麻烦,是有可能会影响职业生涯的,手术治疗是最有效的

...[详细]

-

![[流言板]稳定发挥!克莱](http://cppe9.ahlulin.com/uploads/images/4791970.jpg) [流言板]稳定发挥!克莱-汤普森全场出战25分钟,16中8得20分5板1断由篮球资讯发表在篮球资讯 50212月08日讯 NBA常规赛,独行侠125-118战胜猛龙。全场比赛,克莱-汤普森出战25分钟

...[详细]

[流言板]稳定发挥!克莱-汤普森全场出战25分钟,16中8得20分5板1断由篮球资讯发表在篮球资讯 50212月08日讯 NBA常规赛,独行侠125-118战胜猛龙。全场比赛,克莱-汤普森出战25分钟

...[详细]

-

弗里克:接受停赛事实我需改进我的行为,只希望裁判吹罚尺度一致

12月14日讯 北京时间12月16日凌晨4:00,2024-25赛季西甲联赛第17轮,巴塞罗那将坐镇主场迎战莱加内斯。赛前,巴萨主帅弗里克出席了新闻发布会,他谈到了球队目前的一些情况。关于将对阵莱加内

...[详细]

12月14日讯 北京时间12月16日凌晨4:00,2024-25赛季西甲联赛第17轮,巴塞罗那将坐镇主场迎战莱加内斯。赛前,巴萨主帅弗里克出席了新闻发布会,他谈到了球队目前的一些情况。关于将对阵莱加内

...[详细]

-

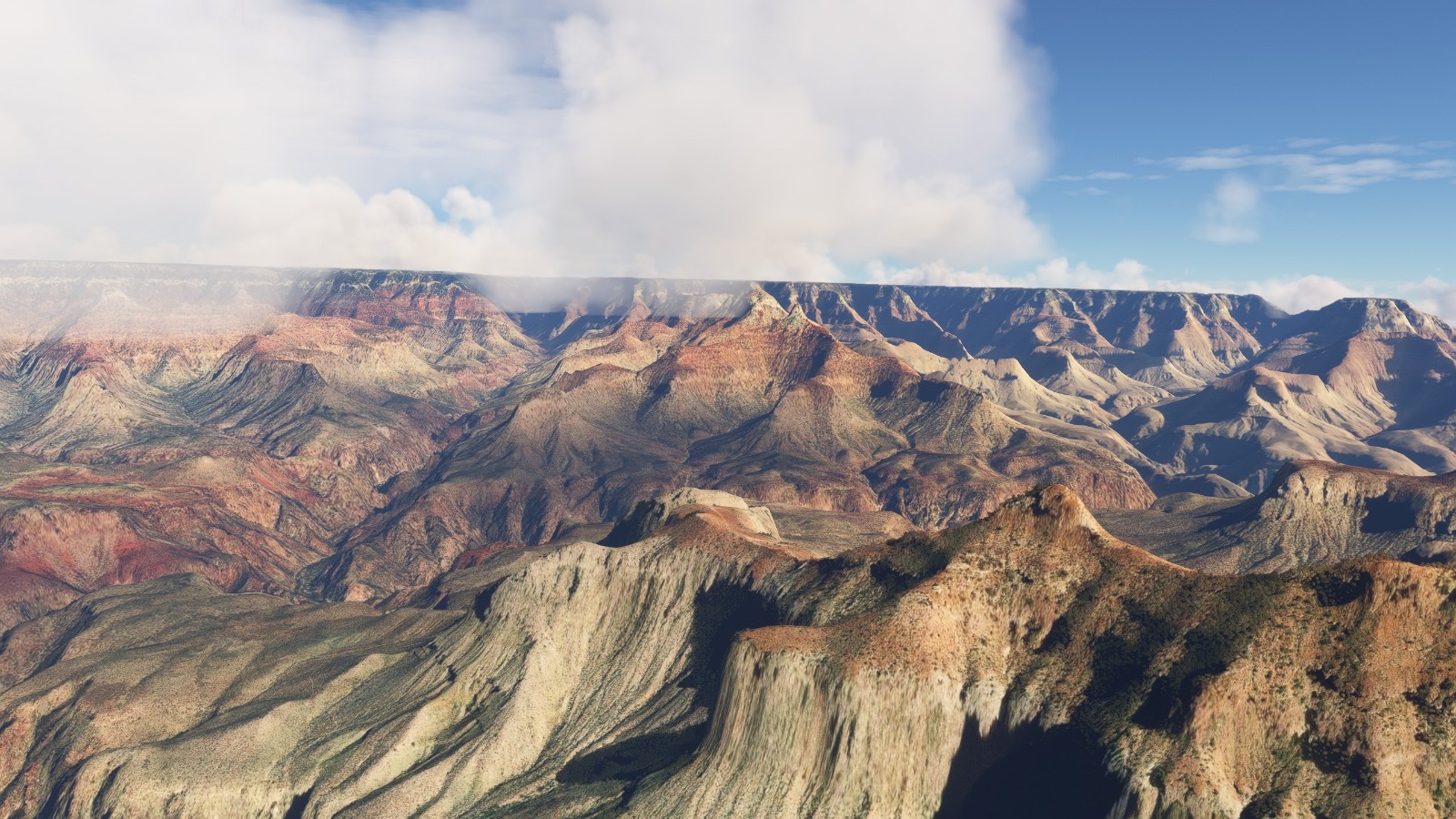

《微软飞行模拟2024》近期已发布,它承诺在视觉效果上相较于2020年发布的原版《微软飞行模拟》会有大幅提升,但它究竟在多大程度上兑现了这一承诺呢?在下方视频中,两款模拟游戏均以1440p分辨率、超高

...[详细]

《微软飞行模拟2024》近期已发布,它承诺在视觉效果上相较于2020年发布的原版《微软飞行模拟》会有大幅提升,但它究竟在多大程度上兑现了这一承诺呢?在下方视频中,两款模拟游戏均以1440p分辨率、超高

...[详细]

美国承认了:对华芯片出口管制是“白费工夫”

美国承认了:对华芯片出口管制是“白费工夫” 《黑神话:悟空》发布全新更新公告 将添加小地图和挑战玩法

《黑神话:悟空》发布全新更新公告 将添加小地图和挑战玩法 本赛季英超创造重大机会榜:利物浦40次居首,切尔西、阿森纳39次

本赛季英超创造重大机会榜:利物浦40次居首,切尔西、阿森纳39次 🤔连续罚丢点球+踢丢超级大单刀,姆巴佩真的丧失信心了吗?

🤔连续罚丢点球+踢丢超级大单刀,姆巴佩真的丧失信心了吗? 比其他专业高几十分!高考601分女生选择殡葬专业引热议:直言好就业

比其他专业高几十分!高考601分女生选择殡葬专业引热议:直言好就业